### LC-DET-2014-001

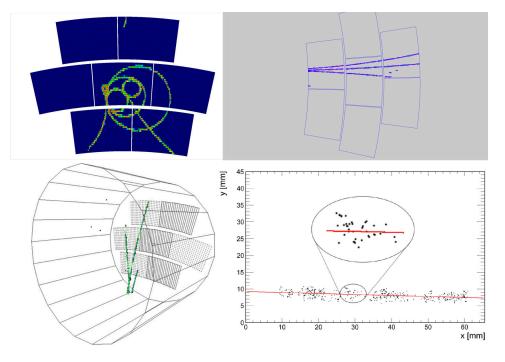

Tracks recorded during test of different modules with the Large Prototype TPC

ECFA DETECTOR R&D PANEL LCTPC REVIEW REPORT

## LCTPC Collaboration

November 3, 2013

# Contents

| 1        | Intr                                     | coduction                                                                                                                                                  | 3        |  |  |  |

|----------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|          | 1.1                                      | LCTPC collaboration                                                                                                                                        | 3        |  |  |  |

|          | 1.2                                      | Motivation for the ILD TPC                                                                                                                                 | 5        |  |  |  |

|          | 1.3                                      | LCTPC testbeam infrastructure                                                                                                                              |          |  |  |  |

|          | 1.4                                      | Institutes                                                                                                                                                 | 8        |  |  |  |

|          |                                          | 1.4.1 Observers                                                                                                                                            | 9        |  |  |  |

| <b>2</b> | 2 Technologies and R&D                   |                                                                                                                                                            |          |  |  |  |

|          | 2.1                                      | Gas Amplification                                                                                                                                          | 0        |  |  |  |

|          |                                          | 2.1.1 Gas Electron Multiplier- GEMs                                                                                                                        | 0        |  |  |  |

|          |                                          | 2.1.2 Micromegas                                                                                                                                           | 1        |  |  |  |

|          |                                          | 2.1.3 Pixelized Readout                                                                                                                                    | 2        |  |  |  |

|          | 2.2                                      | Module Layouts                                                                                                                                             | 3        |  |  |  |

|          |                                          | 2.2.1 Asian Modules                                                                                                                                        | 4        |  |  |  |

|          |                                          | 2.2.2 DESY Modules                                                                                                                                         | 4        |  |  |  |

|          |                                          | 2.2.3 Saclay Modules                                                                                                                                       | 5        |  |  |  |

|          |                                          | 2.2.4 Pixel Modules $\ldots \ldots \ldots$ | 6        |  |  |  |

|          | 2.3 Operation Experience and Performance |                                                                                                                                                            |          |  |  |  |

|          |                                          | 2.3.1 Asian Modules $\ldots \ldots \ldots$ | 8        |  |  |  |

|          |                                          | 2.3.2 DESY Modules                                                                                                                                         | 8        |  |  |  |

|          |                                          | 2.3.3 Saclay Modules                                                                                                                                       | 9        |  |  |  |

|          |                                          | 2.3.4 Pixel Modules                                                                                                                                        | 0        |  |  |  |

|          | 2.4                                      | Field Distortions                                                                                                                                          | 1        |  |  |  |

| 3        | Ion                                      | Back Flow 2                                                                                                                                                | <b>5</b> |  |  |  |

|          | 3.1                                      | Simulation of Ion back flow in ILD TPC                                                                                                                     | 5        |  |  |  |

|          | 3.2                                      | Wire grid                                                                                                                                                  | 6        |  |  |  |

|          | 3.3                                      | GEM gate                                                                                                                                                   | 7        |  |  |  |

|          | 3.4                                      | Conclusion                                                                                                                                                 | 9        |  |  |  |

| 4        | Elec                                     | ctronics 3                                                                                                                                                 | 0        |  |  |  |

|          | 4.1                                      | Introduction                                                                                                                                               | 0        |  |  |  |

|          | 4.2                                      | Requirements                                                                                                                                               | 0        |  |  |  |

|          |                                          |                                                                                                                                                            |          |  |  |  |

|          | 4.3   | Test electronics $\ldots \ldots 31$ |  |

|----------|-------|----------------------------------------------------------------------------------------------------|--|

|          |       | 4.3.1 The ongoing SALTRO16 development                                                             |  |

|          |       | 4.3.2 Micromegas Integration                                                                       |  |

|          | 4.4   | Tentative Roadmap towards the ILD TPC electronics 35                                               |  |

|          |       |                                                                                                    |  |

| <b>5</b> |       | chanics 37                                                                                         |  |

|          | 5.1   | Design of a new Fieldcage                                                                          |  |

|          | 5.2   | Development of a Low-Material TPC Endplate for ILD $\ldots$ 40                                     |  |

|          |       | 5.2.1 Motivation $\ldots \ldots 41$ |  |

|          |       | 5.2.2 Measurements of the LP2 endplate                                                             |  |

|          |       | 5.2.3 Measurements using the ILD endplate model 43                                                 |  |

|          |       | 5.2.4 Issues related to the plate design space-frame 46                                            |  |

|          |       | 5.2.5 Possible issues related to scaling the LP2 design to the                                     |  |

|          |       | ILD endplate 47                                                                                    |  |

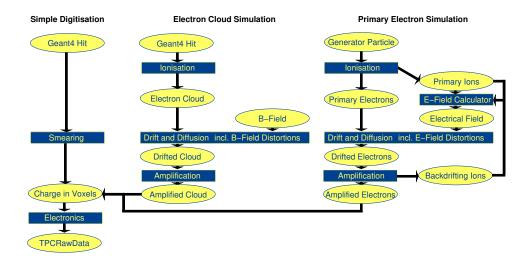

| 6        | Soft  | ware and Simulation 48                                                                             |  |

| Ŭ        | 6.1   | The Software Framework                                                                             |  |

|          | 6.2   | Simulation                                                                                         |  |

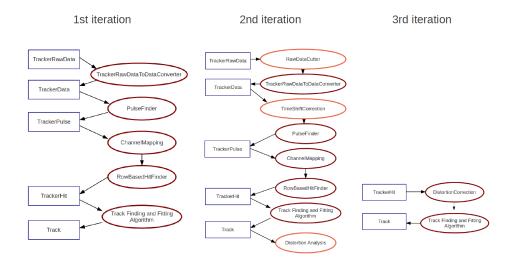

|          | 6.3   | Data Reconstruction   49                                                                           |  |

|          | 0.0   | 6.3.1 Pad Based                                                                                    |  |

|          |       | 6.3.2 Pixel Based                                                                                  |  |

|          |       | 6.3.3 Tracking                                                                                     |  |

|          | 6.4   | Data Analysis         53                                                                           |  |

|          | 6.5   | Conditions Database and Grid Usage                                                                 |  |

|          | 6.6   | Outlook and Tasks                                                                                  |  |

|          | 0.0   |                                                                                                    |  |

| 7        | Out   | look 56                                                                                            |  |

|          | 7.1   | Performance of the ILD TPC                                                                         |  |

|          |       | 7.1.1 Remaining R&D Issues for the next few years 57                                               |  |

|          |       | 7.1.2 The Ion Gate                                                                                 |  |

|          |       | 7.1.3 Issues for the MPGD technologies                                                             |  |

|          |       | 7.1.4 Local distortions                                                                            |  |

|          |       | 7.1.5 Demonstration of power pulsing for the readout elec-                                         |  |

|          |       | tronics $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $59$                        |  |

|          |       | 7.1.6 Cooling of the electronics and temperature control 59                                        |  |

|          |       | 7.1.7 Demonstration of performance at 3.5 T 60                                                     |  |

|          | 7.2   | Engineering design issues for the ILD TPC 60                                                       |  |

|          |       | 7.2.1 Readout electronics                                                                          |  |

|          |       | 7.2.2 Fieldcage and endplates                                                                      |  |

|          |       | 7.2.3 Software                                                                                     |  |

|          | 7.3   | A possible timeline for the ILD TPC R&D                                                            |  |

|          | 7.4   | Conclusions                                                                                        |  |

|          | • • = |                                                                                                    |  |

## Chapter 1

# Introduction

This report is organised as follows. Chapter 1 presents the LCTPC collaboration and its connection to the ILD concept detector proposed for a future Linear Collider (ILC/CLIC). The following chapters describe in more detail the various R&D activities on the different gas multiplication technologies under study (chapter 2), the study of ion backflow (chapter 3), the overall mechanics of the ILD TPC (chapter 5), electronics (chapter 4) and software developments (chapter 6). The report concludes with an outlook for the coming 2-3 years (chapter 7).

## 1.1 LCTPC collaboration

A Time Projection Chamber (TPC) was already foreseen as a central tracker for a detector at the proposed TESLA linear collider [1] in 2001. In October 2001 an initial program of detector research was proposed by the LC TPC group [2] to be reviewed by the DESY PRC. Since then, roughly every second year a status report was prepared for review by the PRC, the last one in 2010 [3]. The PRC duties have since been transferred to the ECFA Detector Panel.

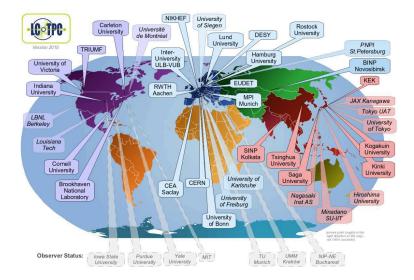

The LCTPC groups formed a collaboration by signing a Memorandum of Agreement (MOA) in 2007, and updates to the MOA appear at the end of each year as an Addendum. The MOA and the Addenda can be found on the LCTPC website [4]. A list of the participating institutes can be found in section 1.4 and is graphically represented in figure 1.1.

Part of the LCTPC organisation are

-Three Regional Coordinators serve as an executive body. One of them is

<sup>-</sup>The Collaboration Board (CB) (one member per institute) as the governing body. Every year the CB elects a member to chair its meetings.

Figure 1.1: Map of the LCTPC collaboration member institutes

chosen as the Spokesperson, currently Jochen Kaminski (Bonn University). –A Speakers Bureau and an Editorial Board to monitor the Large Prototype TPC talks at major conferences and journal paper production.

Since the start of the official collaboration between the ILC (0.2 - 1.0 TeV with superconducting cavities) and CLIC (1.4 - 3.0 TeV with two-beam technology), the LCTPC collaboration has been preparing a TPC for the generic  $e^+e^-$  linear collider (LC). The LCTPC concept already allows for higher energies so that no change is needed in the organizational structure; the parameters of a TPC for ILC (see [5]) are somewhat different from those for CLIC (see [6]).

Recent efforts are underway to have the superconducting linear collider ILC built in Japan. It is envisaged to be realized in two or more stages: first stage, the 250 GeV machine (Higgs' precision measurements), followed by an extension to 500 GeV (top, Higgs' and other precision studies), and finally by an upgrade to ca. 1000 GeV. (Progress is regularly reported in the 'LC Newsline' http://newsline.linearcollider.org.)

In addition, a new leadership arrangement and collaboration, the oversight committee 'Linear Collider Board' and the international 'Linear Collider Collaboration' (LCB and LCC, see the LC Newsline), will replace the structure set up by the International Linear Collider Steering Committee several years ago and guide the construction of the ILC.

## **1.2** Motivation for the ILD TPC

The following is extracted from the ILD DBD report [5]. The first paragraph relates to the ILD detector at large, while the rest of the section is more TPC specific.

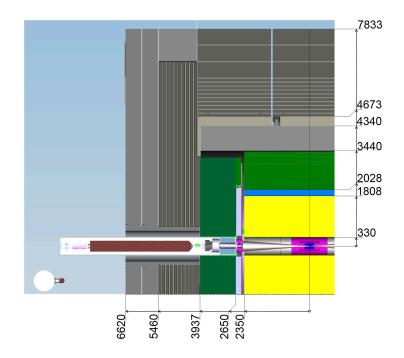

The particle flow paradigm translates into a detector design which stresses the topological reconstruction of events. A direct consequence of this is the need for a detector system which can separate efficiently charged and neutral particles, even inside jets. This emphazises the spatial resolution for all detector systems. A highly granular calorimeter system is combined with a central tracker which stresses redundancy and efficiency. The whole system is immersed in a strong magnetic field of 3.5 T. In addition, efficient reconstruction of secondary vertices and very good momentum resolution for charged particles are essential for an ILC detector. A view of a quarter of the ILD detector concept can be seen in figure 1.2.

Figure 1.2: Quadrant view of the ILD detector concept. The interaction point is in the lower right corner of the picture. Dimensions are in mm. The part in yellow represents the TPC.

A TPC tracker in a linear collider experiment offers several advantages. Tracks can be measured with a large number of three-dimensional  $(r, \phi, z)$  space points. The point resolution,  $\sigma_{\text{point}}$ , and double-hit resolution, which are moderate when compared to silicon detectors, are compensated by continuous tracking. The TPC presents a minimum amount of material as required for the best calorimeter and PFA performance. A low material budget also minimises the effects due to the  $\simeq 10^3$  beamstrahlung photons per bunch-crossing which traverse the barrel region [7]. To obtain good momentum resolution and to suppress backgrounds, the detector will be situated in a strong magnetic field of 3.5 T. Under this condition a point resolution of better than 100  $\mu$ m for the complete drift and a double hit resolution of < 2 mm are possible.

Continuous tracking facilitates the reconstruction of non-pointing tracks which are significant for the particle-flow measurement and for the reconstruction of physics signatures in many scenarios. The TPC yields particle identification via the specific energy loss dE/dx which is valuable for many physics analyses.

Over the past years systematic R&D work to develop the design of a high-resolution TPC for a linear collider detector has been pursued in the context of the LCTPC collaboration [4, 8, 9, 10].

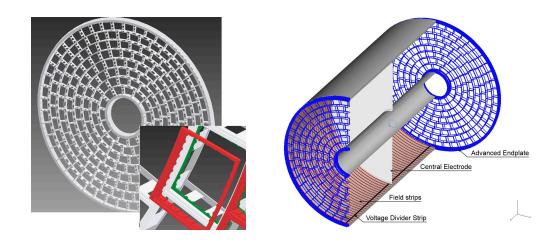

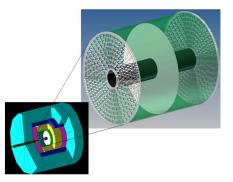

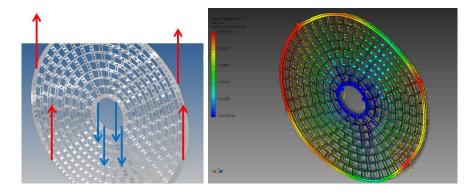

The main parameters for the TPC are summarised in Table 1.1. The readout endplate being a concentric assembly of modules is shown in figure 1.3. The current design of the endplate foresees 240 modules of approximately  $17 \times 22$  cm<sup>2</sup>.

| Parameter                                 |                                                                                                                                                                |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Geometrical parameters                    | $\begin{array}{ccc} \mathrm{r_{in}} & \mathrm{r_{out}} & \mathrm{z} \\ \mathrm{329} \ \mathrm{mm} & 1808 \ \mathrm{mm} & \pm \ 2350 \ \mathrm{mm} \end{array}$ |

| Solid angle coverage                      | Up to $\cos\theta \simeq 0.98$ (10 pad rows)                                                                                                                   |

| TPC material budget                       | $\simeq 0.05 X_0$ including outer fieldcage in r                                                                                                               |

|                                           | $< 0.25 X_0$ for readout endcaps in z                                                                                                                          |

| Number of pads/timebuckets                | $\simeq 1-2 \times 10^6/1000$ per endcap                                                                                                                       |

| Pad pitch/ no.padrows                     | $\simeq 1 \times 6 \text{ mm}^2$ for 220 padrows                                                                                                               |

| $\sigma_{\text{point}} \text{ in } r\phi$ | $\simeq 60 \ \mu m$ for zero drift, $< 100 \ \mu m$ overall                                                                                                    |

| $\sigma_{\rm point}$ in $rz$              | $\simeq 0.4 - 1.4 \text{ mm} (\text{for zero} - \text{full drift})$                                                                                            |

| 2-hit resolution in $r\phi$               | $\simeq 2 \text{ mm}$                                                                                                                                          |

| 2-hit resolution in $rz$                  | $\simeq 6 \text{ mm}$                                                                                                                                          |

| dE/dx resolution                          | $\simeq 5~\%$                                                                                                                                                  |

| Momentum resolution at B= $3.5$ T         | $\delta(1/p_t) \simeq 10^{-4}/\text{GeV/c} \text{ (TPC only)}$                                                                                                 |

Table 1.1: Performance and design parameters for the TPC with standard electronics and pads. The momentum resolution of the full ILD tracking system is  $\simeq 2 \times 10^{-5}/\text{GeV/c}$ .

Figure 1.3: Left: Drawing of the proposed end-plate for the TPC. In the insert a backframe which is supporting the actual readout module, is shown. Right: Conceptual sketch of the TPC system showing the main parts of the TPC (not to scale).

## 1.3 LCTPC testbeam infrastructure

The setup in the DESY II testbeam area T24/1 consists of a large field cage with a modular endplate, allowing up to 7 detector modules to be mounted (Large Prototype TPC). The LP TPC can be inserted in the PCMAG superconducting magnet, which is mounted on a movable lifting stage (3 axes). High Voltage and gas supplies and corresponding slow control systems are available, as well as cosmic and beam scintillation counters trigger system. A laser calibration system has been used already in 2009 and is being recommissioned. A system of external silicon layers in the narrow space between the TPC and the magnet inner wall is still under consideration.

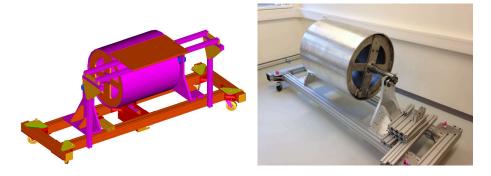

The fieldcage is made of light weight composite materials. Its diameter is 72 cm and the maximum drift distance is 57 cm. Figure 1.4 shows a picture of the magnet PCMAG inside the movable lifting stage (on the left) together with a view of the LP TPC with 7 Micromegas modules mounted (on the right).

Before 2012 the PCMAG magnet (on loan from KEK) had to be filled

Figure 1.4: Left: PCMAG mounted on a movable lifting stage in the DESY testbeam area. Right: Seven micromegas modules mounted on the endplate of the LP, equipped with highly integrated electronics.

manually with liquid He from a dewar. Between July 2011 and April 2012 the magnet was shipped back to Japan and modified to run without liquid He using two cryo coolers and two He gas compressors. The upgraded system has been in operation since June 2012.

### 1.4 Institutes

Groups in the three global regions which have signaled interest in participating in the LCTPC R&D are listed here.

Americas

Carleton Univ & TRIUMF, Ottawa, ON K1S 5B6, Canada Univ. de Montreal, Montreal, PQ H3C 3J7, Canada Univ. of Victoria & TRIUMF, Victoria, BC V8W 3P6, Canada Brookhaven National Laboratory, Upton, NY 11973-5000, USA Cornell Univ., Ithaca, NY 14853-5002, USA Indiana Univ., Bloomington, IN 47405, USA Lawrence Berkeley National Lab., Berkeley, CA 94720-8153, USA Asia Tsinghua Univ., Beijing 100084, China Saha Inst. of Nucl. Phys., Kolkata 700064, India Hiroshima Univ., Higashi-Hiroshima, Hiroshima 739-8526, Japan KEK, Tsukuba, Ibaraki 305-0801, Japan Kinki Univ., Higashi-Osaka, Osaka 577-8502, Japan Kogakuin Univ., 1-24-2, Nishi-Shinjuku, Shinjuku, Tokyo 163-8677, Japan Faculty of Informatics, Nagasaki Inst. of Applied Science NiAS, Nagasaki 851-0193, Japan Saga Univ., Faculty of Science and Engineering, Honjo, Saga 840-8502, Japan Tokyo Univ. Agriculture and Technology, Koganei, Tokyo 184-8588, Japan Univ. of Tokyo, ICEPP, Tokyo 113-0033, Japan

#### Europe

IIHE (Inter-university Institute for High Energies) ULB-VUB, B-1050 Bruxelles

CEA Saclay, Irfu, F-91191 Gif-sur-Yvette, France

RWTH Aachen, D-52056 Aachen, Germany

Univ. Bonn, D-53115 Bonn, Germany

DESY Hamburg, Notkestrasse 85, D-22607 Hamburg, Germany

Albert-Ludwigs Univ., D-79104 Freiburg, Germany

Taras Shevchenko National University of Kyiv, 01601 Kyiv, Ukraine

Univ. Hamburg, Inst. für Experimentalphysik, D-22761 Hamburg, Germany

Max-Plank-Inst. für Physik, D-80805 Munich, Germany

Univ. Rostock, D-18051 Rostock, Germany

Univ. Siegen, D-57068 Siegen, Germany

NIKHEF, NL-1009 DB Amsterdam, Netherlands

Budker Inst. of Nuclear Physics, RU-630090 Novosibirsk, Russia

Lund University, Dept. of Physics, Box 118, S-221 00 Lund, Sweden

CERN, CH-1211 Geneva 23, Switzerland

#### 1.4.1 Observers

'Oberservers' are groups or persons that could not sign the MOA but want to be informed as to the progress, thus are included in the LCTPC mailing list:

Iowa State, MIT, Purdue, Yale, Louisiana Tech, JAX Kanagawa, Mindanao, LAL Orsay/IPN Orsay, TU Munich, Karlsruhe, UMM Krakow, Bucharest, St.Petersburg.

## Chapter 2

# Technologies and R&D

Various readout techniques are being studied to find the best option for the ILD TPC. These techniques were first tested in small prototypes at different institutes, but are now implemented in larger modules designed to fit into the Large Prototype at DESY [4].

### 2.1 Gas Amplification

Time Projection Chambers, which are in operation today or have been operated in the past were read out by multi-wire proportional chambers. However, the stringent requirements stated in chapter 1 can not be fulfilled with such a readout. The strong magnetic field of B = 4 T and the wide gap of 1-2 mm between wires leads to strong  $E \times B$ -effects. It was demonstrated in reference [11] that it is not possible to reach the required spatial resolution with a wire-based readout. The LCTPC collaboration has, therefore, investigated the use of Micropattern gaseous detectors to replace the MWPCs. The two most widely used MPGDs are Gas Electron Multipliers (GEMs) invented by F. Sauli [12] and Micromegas invented by Y. Giomataris and collaborators [13]. All MPGDs have the advantage of small pitches of order 10-100 µm between sensitive areas. This improves the spatial resolution and significantly reduces  $E \times B$ -effects. Additionally, the charge collection times are much shorter, since in GEMs only the electrons contribute to the signal and in Micromegas the slow ions have to drift only a short distance. Finally, a large fraction of the ions are guided to an electrode and are neutralized there. Thus, the number of ions potentially reaching the drift volume is greatly reduced.

#### 2.1.1 Gas Electron Multiplier- GEMs

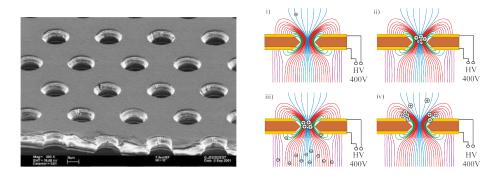

GEMs are foils made of a metal-insulator-metal sandwich. Standard CERN GEM use a 3  $\mu$ m copper layer on both sides of a 50  $\mu$ m kapton layer. A

Figure 2.1: Left: SEM picture of a GEM foil, right: Schematic drawing of the working principle of a GEM [14].

hexagonal hole pattern is etched in the sandwich creating holes with a diameter of 60-70  $\mu$ m at a pitch of 140  $\mu$ m (SEM picture see figure 2.1 left). If an electrical potential is applied to the electrodes, strong electrical fields are created inside the holes and electrons entering a hole initiate a gas amplification avalanche (see figure 2.1 right). The electrons are released in the gas volume below and can either be collected on a pad or multiplied in a further gas amplification stage. Stacking several GEMs has many advantages. One is the reduction of the discharge probability: In the transfer gaps between the GEMs the charge is distributed over more holes reducing the charge density in the following amplification stage.

#### 2.1.2 Micromegas

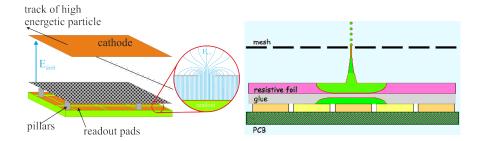

Micromegas consist of a mesh mounted at a short distance  $(50-200 \ \mu m)$  above the readout plane. The mesh is put on a lower electrical potential than the pads and the resulting electrical field is strong enough for gas amplification. If electrons enter the amplification gap from the conversion and drift volume, a very narrow signal is created, since the diffusion in the amplification gap adds only about 20 µm to the signal width. Therefore, the Micromegas are well adapted for detectors with fine readout pads. But in case of pitches in the order of several millimeters, the spatial resolution degrades rapidly, since only one pad is hit giving a resolution of pad pitch/ $\sqrt{12}$ . To improve the performance a new idea was pioneered in the LCTPC collaboration: The readout electrode is covered with a resistive layer grounded at the edges of the module [15] (see also section 2.2.3). Since the layer is disconnected from the pad by an insulating layer of glue, the signal can only be transmitted via capacitive coupling to the pads, while the charge propagates towards the module edge. In this way, the signal is spread over several pads and a more precise position determination is possible.

Figure 2.2: Left: Schematic drawing of the Micromegas detector working principle [14], right: Schematic drawing of a Micromegas detector with resistive anode [15].

#### 2.1.3 Pixelized Readout

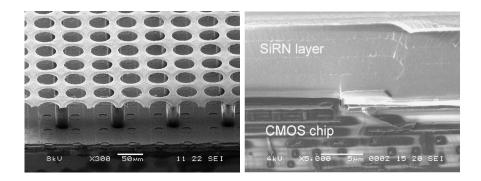

The fine pitch of the Micropattern Gaseous detectors allows for a better resolution of the primary charge than is possible with square-millimeter-size pads or long fine pitched strips. To adapt the feature size of the readout plane to the feature size of the gas-amplification stage, readout chips of a pixel detector are used as an active anode [17]. The bump bond pads usually used to connect the readout chip to the Si-sensor are used as charge collection pads and are placed directly below the gas amplification stage. The Timepix ASIC [18] is currently the preferred chip and is used by several groups.

To protect the ASIC from destructive discharges the active area is covered with an 8 µm thick resistive layer of silicon-richnitride (SiRN) [19]. In case of a discharge the charge does not enter directly into one or more pixel, but is collected on the resistive layer, stopping the discharge at an earlier stage by lowering the electric field between grid and layer. In addition, the charge is spread over a larger area and thus more pixels, reducing the probability of reaching destructive energies. The InGrid [20] itself is produced with photolithographic processes. The important feature is, that with modern post processing techniques the alignment can be done with excellent precision, so that each grid hole can be placed directly above a pixel of the ASIC. Therefore, the holes have a pitch of 55 µm and a diameter of about 30 µm.

Because of the small pixel size and the digitization close to the charge collection pad, the electronic noise is very low (ENC  $\approx 90 \ e^-$ ) and thresholds well below 1000  $e^-$  can be applied. Since InGrids can easily reach gas gains of 5000 a very high detection efficiency of primary electrons is possible. If the primary charge is sufficiently spread due to the diffusion, then primary electrons are likely to enter in separate holes and every hit on a pixel corresponds to the detection of one primary electron.

The first InGrids were produced at the University of Twente. Because of limitations in the size of some machines, the process could not be applied

Figure 2.3: Left: SEM picture of an InGrid detector, right: Cross-section SEM picture of Timepix chip covered with 9 µm SiRN [19].

to full wafers, but only up to 9 chips at a time. To demonstrate that the coverage of a large area with InGrids can be done, the Universities of Bonn and Twente have established a new wafer-based process at the Fraunhofer Institute IZM at Berlin. Now, wafers with 107 InGrids each can be produced at the same time, providing a larger number of detectors for testing.

## 2.2 Module Layouts

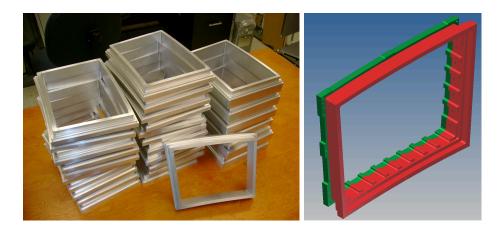

The general module design is similar for all readout techniques. An aluminum backframe serves as a basis and will be used to mount the module on the endplate and ensure gas tightness with an O-ring. The backframes have a keystone like shape of the dimension  $17 \times 22$  cm<sup>2</sup>. They are made of aluminum and are two times cold shocked during the production to re-

Figure 2.4: Left: First batch of backframes before delivery, right: 3D-model of a second version backframe. In red the backframe is shown and in green a mounting bracket necessary to fix the backframe to the endplate.

duce the mechanical stress and provide a precise basis stable in time for the modules. The modules are required to have an overall height of 45 mm. Therefore, the backframes were made with different heights varying from 27 to 41.8 mm to compensate for the different thicknesses of the gas amplification stages (see figure 2.4 left). A second version of the backframe was produced, where some material was reduced (see figure 2.4 right).

Multi-layer readout boards are glued on the backframes. To ensure a good knowledge of the board position, the alignment is done with two precision pins. In the case of a pad based readout, the signals are routed from the pads pointing to the inside of the detector to the connectors on the backside of the PCB, where the readout electronics will be situated. Finally, the gas amplification stage is mounted on the pad plane. Here different approaches have been tested to reduce insensitive area, to give sufficient support to the structure and to distribute the high voltage.

#### 2.2.1 Asian Modules

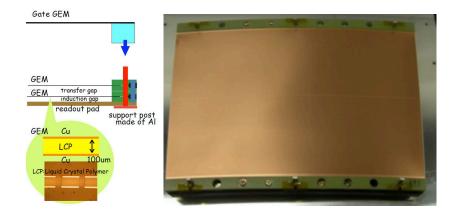

The Asian modules use GEM stacks as a gas amplification stage and are optimized to reduce the insensitive area on the sides of the modules which point towards the detector center. Particles from the interaction point flying between the modules may not be detected if they are very stiff. Therefore, the Asian module foresees no frame along the sides and extends the sensitive area up to the edge of the backframe. To ensure a flat mounting of the GEMs, they are stretched on both arcs and are made of a stiffer material: GEMs with an insulator of 100 µm Liquid Crystal Polymer (LCP) covered with 5  $\mu$ m copper on both sides were produced by SciEnergy. The holes were produced with  $CO_2$  laser drilling and the GEMs were carefully cleaned by dry etching to remove potentially conductive residuals from the holes. The hole pattern is identical to standard CERN GEMs. Because of the thicker material also higher gas gains per GEM can be reached and a double GEM structure is sufficient. The two GEMs are mounted with an induction gap of 2 mm and a transfer gap 3 mm (see figure 2.5 left). The pads have a size of  $1.2 \times 5.4 \text{ mm}^2$  and there are 28 pad rows with a total of 5152 pads.

From the beginning the use of an ion gate (see chapter 3) was envisaged and, thus, the level of GEM1 was planned to be 1 cm below the nominal module height allowing for a later addition of the gate. To absorb the strength necessary to stretch the GEMs and the gate, strong metal poles were implemented at the top and bottom arch.

#### 2.2.2 DESY Modules

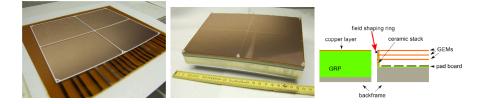

The DESY modules are based on a stack of three standard CERN GEMs, which are divided into 4 quadrants to reduce the electrical energy stored in each sector to avoid destructive discharges. Also for these modules the in-

Figure 2.5: Left: Schematic drawing of the Asian module, right: Photograph of the Asian module.

Figure 2.6: Left: DESY GEM during the mounting of a grid, middle: DESY module, right: cross section of the DESY module and neighboring dummy module used during tests.

sensitive area was minimized as much as possible, but without the emphasis on the side edges. Therefore, in contrast to the Asian approach no force is applied to stretch the GEMs in a frame, but the GEMs are glued to a 1 mm wide ceramic mounting grid, which supports the GEMs not only at the edges, but also with two central bars, where the separation of the GEM sectors already provide an insensitive area. The GEMs are mounted with transfer gaps of 2 mm and an induction gap of 3 mm on a the pad plane. The pads have a size of  $1.26 \times 5.85 \text{ mm}^2$  and there are 28 pad rows with a total of 4829 pads covering about 94 % of the module area.

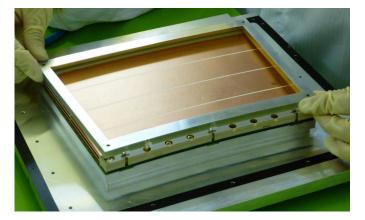

#### 2.2.3 Saclay Modules

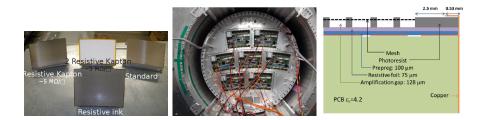

Saclay has developed modules based on Micromegas with a resistive coverage of the pads. While both GEM modules used the ALTRO electronics as a readout, the Micromegas module used the AFTER chip in its readout chain. Since the packing of the AFTER chip was more challenging, and a limited number of channels was available - it was required to cover at least seven modules - larger pads of the size  $3 \times 7 \text{ mm}^2$  were chosen. These were placed in 24 rows with 72 pads each giving a total number of 1728 pads per module.

Figure 2.7: Left: 4 modules with different resistive layers, middle: 7 modules of the production series mounted in the Large Prototype, right: Schematic drawing of the border of the modules.[23]

In a first iteration two different resistive materials, resistive ink and carbon loaded kapton (CLK), and different resistivities,  $3 \text{ M}\Omega/\Box$  and  $5 \text{ M}\Omega/\Box$ , were tested. The CLK proved more homogenous and was therefore preferred in later modules. For the given pad size, the resistivity of  $3 \text{ M}\Omega/\Box$  was best suited, but needs to be adapted, if different pad sizes are chosen. The resistive foil is pressed on the pad plane and the Micromegas is built on top of the resistive layer. Following the Bulk-Micromegas instruction [21] an amplification gap of 128 µm was used. A very good grid homogeneity was reached and a homogeneous gas gain throughout all modules could be demonstrated in dedicated calibration runs with an <sup>55</sup>Fe source, see reference [23].

The HV contact is realized on 2 dedicated pads in the sensitive area. In this way the sensitive area could be extended almost to the edge of the modules, limited only by a 3 mm wide frame made of photoresist, which holds the grid. The ground connection of the resisitive layer extends over the edge of the module and covers both the side of the module and also the frame of the module (see figure 2.7 right).

After establishing the technology a production series of 9 modules including a highly integrated electronics (see chapter 4) followed. Seven of the modules were used simultaneously in the Large Prototype. The experience of a quasi industrial production, where the pad plane and electronics PCBs were produced by ELTOS [22] and the resistive layer and Bulk-Micromegas were applied at the CERN workshop, was very positive and the quality of the modules was as high as on the prototype level. The complete module has an average radiation length of 21.38  $\frac{g}{cm^2}$ .

#### 2.2.4 Pixel Modules

Two different modules with InGrid readout have been constructed, but both modules feature only a small area covered with InGrids. They both have a single PCB, on which 8 InGrids can be mounted (see figure 2.8 left). The first module was built in 2010 by Saclay and NIKHEF (see figure 2.8 middle).

Figure 2.8: Left: PCB 'Octopuce' with 8 InGrids mounted, middle: First module with InGrids, right: Second module with InGrids.

The InGrids had been made at the University of Twente and the readout was a NIKHEF-built readout system MUROS2.0. The InGrids were mounted about 1 mm below the nominal height and a field termination plate was placed around the InGrids at the correct height. The small height difference was necessary to reduce the opening in the plate to the size of the active area of the InGrids and to cover the remaining area of the PCB, including the bond wires and HV supply lines. This arrangement reduces the local field distortions around the InGrids

To demonstrate that the coverage of a large area with InGrids is possible, the University of Bonn has initiated the above-mentioned wafer-based production of the InGrids. Also, a readout system is being developing which allows an easy scaling of the number of readout Timepix chips. The system is based on the Scalable Readout System (SRS) developed by the RD51 collaboration. To adapt the SRS, the FPGA code needs to be rewritten for the communication with the Timepix chip, and special adapter PCBs are necessary to combine and transfer the communication and data signals to and from the chip. The system can now be operated, but several features still await implementation and several further optimizations are planned.

To test these new developments on a smaller scale a second module with 8 InGrids was built in 2013 (see figure 2.8) and successfully operated in the Large Prototype.

## 2.3 Operation Experience and Performance

All modules have been tested in the Large Prototype at DESY. While each of the pad-based module was tested several times and optimized, both InGrid modules have been tested only during a short test beam campaign. The experience gained during all test beam periods as well as the best transverse spatial resolutions are shown in this section.

All groups have used the same gas mixture of  $Ar:C_4:iC_4H_{10}$  95:3:2. The electric drift field was set in most cases to E = 230 V/cm, which is close to the maximum of the drift velocity, and alternatively to E = 130 V/cm, which is the minimum of the transverse diffusion.

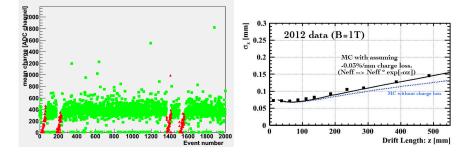

Figure 2.9: Left: Mean charge per hit in dependence on the event number. In red are events with reduced gain, which is likely because of a discharge, right: transverse spatial resolution of the best pad row in dependence on the drift distance. The dotted and solid lines are calculations with the analytic model with the charge loss switch on and off.

#### 2.3.1 Asian Modules

The Asian group has built three modules from the beginning and has made several test beam periods at DESY (2009, 2010, 2012). The first campaigns were dominated by very strong field distortions because of the mounting pins and the bare frames. After introducing the field shaper, the distortions are comparable to the ones of other modules. One other important observation was a high number of discharges and HV glitches on the GEMs. Figure 2.9 shows the gain drops clearly visible in the histogram of mean charge per hit. To minimize the energy released in a discharge, the GEMs were segmented into four arches, each with an area of about 100 cm<sup>2</sup>.

The transverse spatial resolution is shown in figure 2.9 right, where the spatial resolution of a single row in the middle of a module is shown. In this context an analytical formula was developed to predict the spatial resolution of a TPC. This formula includes not only the effect of diffusion, angle, noise and a finite pad-size, but also the influence of the electronics threshold, number of effective primary electrons, the Polya-parameter of the gas amplification, cross talk between pads and signal lines, charge loss because of attachment and the pad response function are taken into account. All these parameters can be varied and, if correctly chosen, describe well the measured data (see blue line in figure 2.9 right).

#### 2.3.2 DESY Modules

First tests with the GridGEMs were in 2011, where a simplified readout board featuring about 900 nominal pads was used. These functionality tests disclosed several shortcomings in the HV distribution, leading also to the destruction of several GEMs. The shortcomings were identified and solved in the final design. Three modules were built and tested in 2012 and 2013.

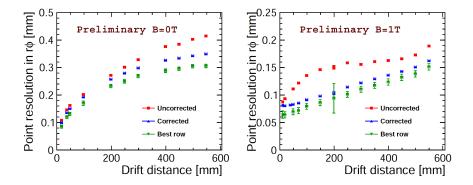

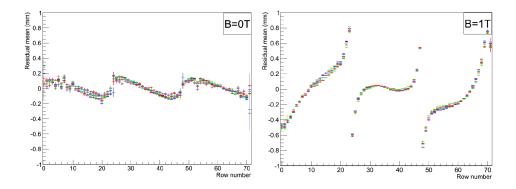

Figure 2.10: Left: transverse spatial resolution with B = 0 T, right: Transverse spatial resolution with B = 1 T. [16]

Since only a limited number of the readout channels was available each of the modules was equipped with about 2,400 channels, so that a continuous completely equipped area about 10 cm wide and 50 cm long was available for recording events.

During the data taking campaign in 2013 a large data set of more than  $10^6$  events was recorded. The transverse spatial resolution without (left) and with (right) a magnetic field is shown in figure 2.10. The figure shows in red uncorrected data, in blue data that was corrected for the field distortion described in section 2.4. For this a data driven approach correcting every hit by the mean offset recorded for the relevant pad row was used. Finally, the best pad row (row 16 in the middle of the central module) was used indicating the best possible performance in the case of almost no field distortions.

#### 2.3.3 Saclay Modules

Saclay has organized seven test beam periods between 2008 and 2013 (see reference [23] for more details). After determining the best resistive cover of the pads in 2008-2010, the final design and the small series production was tested in 2012 and 2013. During the first test beam major problems with the connector between the pad plane and the readout electronics occurred and a large fraction of the pads became disconnected. This problem was solved during the second test beam campaign and a large data sample of more than  $10^6$  tracks was collected.

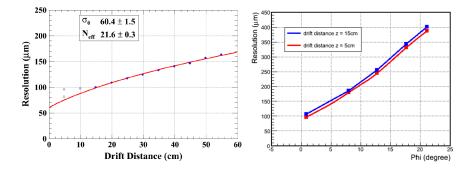

The transverse spatial resolution is shown in dependence on the drift distance in figure 2.11 left. The open symbols at the beginning were taken at a later time and show a worse resolution than expected. This might be because some environmental parameters like temperature or gas pressure changed in the meantime and the gas amplification was lowered. The closed symbols were included in the fit and give a good value for  $N_{eff}$  and the

Figure 2.11: Results of the Micromegas module. Left: Transverse spatial resolution in dependence on the drift distance in B = 1 T. Right: Transverse spatial resolution in dependence on the track inclination  $\phi$ . [23]

intrinsic detector resolution  $\sigma_0$ .

For better comparison between the GEM and Micromegas gas amplification stage, a pre-series module was equipped with the ALTRO electronics this year and a short test beam campaign was used to take data. A vital interest was the shorter shaping time of down to 30 ns, which is possible only with the ATLRO electronics, while the AFTER electronics has a minimum shaping time of 100 ns. The data, however, has not been analyzed yet.

#### 2.3.4 Pixel Modules

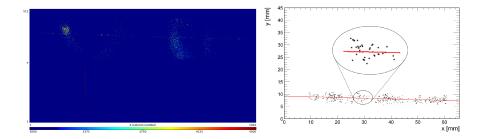

The first InGrid module functioned well except that one of the InGrids was prone to discharges and only a low gas amplification could be reached. To keep the electric field distortions in an acceptable limit, the HV of the other InGrids had to be kept at the same potential. Therefore, the efficiency of the complete module was reduced. Nevertheless, tracks could be identified (see figure 2.12 left).

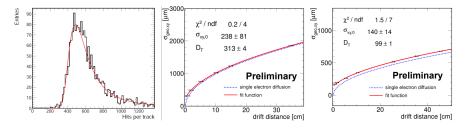

On the second module one Timepix ASIC showed a rather high noise level which could not be reduced. Because of this the threshold of this chip was set to a high level leaving this chip quasi insensitive, but not affecting the remaining chips. Besides, a large cross talk could be observed in many events. These events could be identified and removed from the analysis leaving sufficient good events such as depicted in figure 2.12 right. Even though the track length was only 5.6 cm, the analysis shows that a large number of electrons can be associated with each track (see figure 2.13 left) and the spatial resolution follows the single electron diffusion limit both with and without magnetic field (see figure 2.13 middle and right.) In this plot, the spatial resolution has been plotted for all electrons without correction. The large intrinsic detector resolution  $\sigma_{xy,0}$  of 100-200 µm are caused by the field distortions around the InGrids as described in the next section.

Figure 2.12: Left: Track of a 5 GeV electron in  $\text{He:iC}_4\text{H}_{10}$  recorded by the first InGrid module, right: Track of a 5 GeV electron in  $\text{Ar:CF}_4:\text{iC}_4\text{H}_{10}$  95:3:2 recorded by the second InGrid module. The red line visualizes the reconstructed track.

Figure 2.13: Left: Number of electrons associated with tracks of 5.6 cm with an InGrid module, middle: transverse spatial resolution dependence on the drift distance with B = 0 T (middle), and B = 1 T (right).

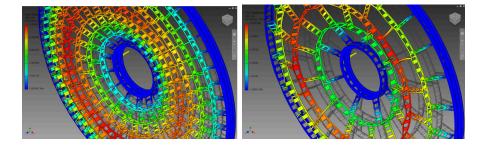

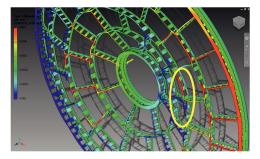

## 2.4 Field Distortions

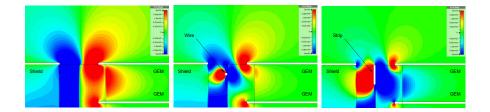

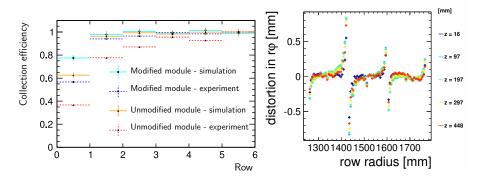

All modules experience strong local field distortions at the module edges. A detailed simulation with CST and Garfield++ confirmed the suspicion, that underlaying lower potentials leak through the gaps between modules and cause the field distortions. Figure 2.14 left shows the electrical field at a transition between a dummy module and a DESY module. In the study 200 electrons were emitted at each of 50 equidistant points along a line perpendicular to the module edge. It was counted how many of these electrons are collected on a readout pad and how many are lost. The efficiency loss of the first 3 pad rows is clearly visible in figure 2.15 left and of the same magnitude as in the data collected in the experiment. To compensate the loss of charge, different forms of additional electrodes on the side of the module were studied. In figure 2.14 middle, the electric field can be seen when a thin wire (diameter of  $150 \ \mu m$ ) is attached to the side, and in figure 2.14 right the influence of a broader strip is shown. For the last test beam period, a wire was glued to the sides and put on the same potential as the topmost electrode of the GEM stack. As expected from simulations the efficiency drop observed at the first 2 rows of the module is

Figure 2.14: CST calculation of the field distortions around the DESY module. Left: without modification, middle: with a 150 µm thick wire around the module, right: with a 1 mm wide strip around the module.

Figure 2.15: Left: charge collection efficiency in dependence on the row number in simulations and measurements with the DESY module. Right: Mean deviations of the charge from the track for different drift distances in dependence on the module row radius.

reduced by a factor of 2 (see figure 2.15 left). Despite this improvement the field distortions still have a major impact on the drift path of the primary electrons and the measured charge shows deviations from the reconstructed tracks. As an example in figure 2.15 right the mean deviation from the track is shown.

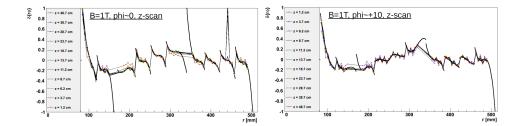

Similar observations were made with the Asian module (see figure 2.16 left), where small track distortions could be observed even between the GEM sectors and significant larger distortions at the module edges. In contrast to the DESY module, the segmentation of the Asian GEMs is on the side of the drift volume and therefore influences the drift of the primary electrons longer. In upcoming modules, the GEMs will be turned, so that the unsegmented side will point towards the drift volume. Figure 2.16 right and figure 2.17 left show very similar data, but with tracks inclined to either the right or left by 10°. The inclination increases the track distortions, because in this case the primary electrons are displaced from the original position not along the track, but at a given angle. Therefore, the charge broadening due to the electrical field distortions and  $E \times B$  effect not only leads to a

Figure 2.16: Mean deviations of the charge from the track in dependence on the row number for the Asian module. Left:  $0^{\circ}$ , right:  $+10^{\circ}$

Figure 2.17: Left: Mean deviations of the charge from the track in dependence on the row number for the Asian module with inclination of  $-10^{\circ}$ . Right: Mean deviations of the charge from the track in dependence on the position on the chip for the second InGrid module.

broader signal, but also to an additional displacement of the charge center. This effect is observed for all modules.

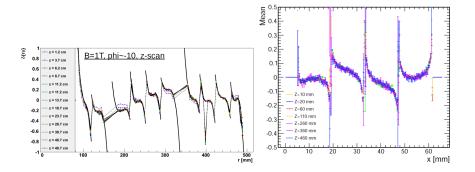

Also with the Micromegas module distortions due to field inhomogeneities were observed. In figure 2.18, the large impact of the magnetic field, which creates additional  $E \times B$ -effects is clearly visible. In case of the Micromegas, the track distortions without magnetic field is visible even for track inclinations of 0°. The origin of these distortions is still under investigation.

InGrid modules show the same deviations at each transition from InGrid to InGrid (see figure 2.17 right). Summarizing the observation of all different techniques is, that the field distortions were observed, if some lower potential (in particular ground) was not covered by a field termination plate, but a gap was left. In a first approximation the track distortions were found to be independent of the drift distance (> 1 cm) and thus originate only of local field inhomogeneities in the vicinity of the modules. As a first approach the displacement of the center was averaged over all drift distances. In a second iteration of the reconstruction the centers were corrected for the average displacement. This is however only possible for a specific set of tracks with identical inclination. For a long term use, the field distortions need to be

Figure 2.18: Mean deviations of the charge from the track in dependence on the row number for the Saclay modules. Left: B = 0 T, right: B = 1 T.

reduced and a complete model needs to be developed to correct for the remaining effects.

## Chapter 3

# Ion Back Flow

## 3.1 Simulation of Ion back flow in ILD TPC

Positive ions drifting back into the gas volume of the TPC is a well known issue for wire chambers. For MPGDs, the amount of ions drifting back is much lower, but can still be significant with a high track density.

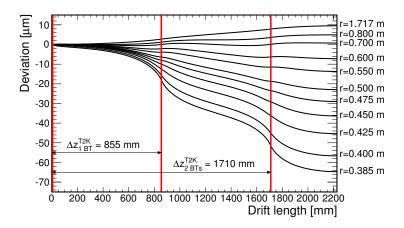

Simulations have been done by D. Arai and T. Krautscheid, using the expected background in ILC, to evaluate the electrons displacement due to the electric field distortion induced by the ions. Due to the bunch-train structure of the beam of ILC (one 1 ms train every 200 ms), the ions from amplification will be concentrated in discs of about 1 cm thickness near the readout, and then drift back into the drift volume. There would be three such discs in the chamber in normal operation. Figure 3.1 shows the azimuthal displacement of electrons for different radial positions in the chamber.

Figure 3.1: Displacement due to positive ions.

These simulations assume a back flow rate of unity, which means that

for every drift electron, only one positive ion drifts back. The amount of displacement should therefore be multiplied by the actual rate of the amplification system. It is obvious that a rate of one cannot possibly be achieved, so that distortions larger than 60 µm in parts of the TPC are unavoidable without a gate.

To cope with the resolution requirements of the ILD TPC, these distortions need to be either corrected or suppressed with an ion gating system. The fluctuations of the pair background in the TPC might be very large and render it impossible to make reliable corrections. Besides, the bunch-train configuration of ILC gives an ideal time structure for gating. The positive ions will drift about 1 cm during the 1 ms readout of a bunch train. There is then about 200 ms available to neutralise them. We therefore studied different possibilities to install a gating system in the TPC.

### 3.2 Wire grid

The first possible solution for a gate is the traditional wire technology. In order to minimise the angular dead spaces, and accomodate our module concept, the wires would have to be strung in the radial direction. Simple field calculations shown in reference [24] show that such a structure would have very little effect on the electron trajectories in the open configuration. There could be an angular effect due to the loss of electrons on the wires, but since the diffusion is typically larger than the wire width, this effect will be small.

There are two possible voltage schemes for the "closed" configuration of the wire gate:

- **Single potential** By increasing the potential on all the wires, the drift field between the gate and the amplification is reversed. The positive ions will then drift back and be neutralised on the MPGD. This requires a fairly high voltage in the gate (several 100 V). The voltage will depend strongly on the distance of the gate from the MPGD, as shown in figure 3.2a-b).

- Alternate potential By shifting the voltage alternately on every second wire, we can create an electric field (see figure 3.2c) that will make the ions drift towards the wires, where they will be neutralised. The voltages required are relatively small and strongly dependent on the wire spacing. This allows the gate to be slightly closer and switch faster, but it requires a more sophisticated structure to have two electrically isolated grids.

A wire gate is a well understood technology. A prototype gate fitting the Asian GEM module has been produced (figure 3.3). A set of 25  $\mu$ m wire are spot welded on a stainless steel structure. This allows only a single

Figure 3.2: Electric field lines for closed gate configurations. (a) Single potential closed at the level of the gate. The red lines represent the different orientation of the electric field. (b) Single potential closed 2 mm below the gate. The field is much weaker below the gate. (c) Alternate potential. The field below the gate is the same as the drift field.

potential scheme, and the frame is too thick and would create large dead area. This prototype will be used to test the influence of the wire gate on the electron drift trajectories when the gate is open. Further studies are needed to realize a favorable mechanical structure with a thinner frame.

Figure 3.3: Prototype of wire gate installed on an Asian GEM module.

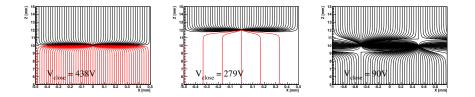

## 3.3 GEM gate

As an alternate gating solution, a GEM based system has been investigated. The use of a GEM makes it easier to integrate it into modules which are already designed for such technology. The two potential planes of the GEM makes it very easy to close the gate by changing the voltage of the lower electrode by a few volts and inverting the electric field in the holes of the GEMs. On the other hand, the open configuration will offer a reduced electron transparency, hence reducing the point resolution. A detailled study of the GEM gate through simulations can be found in reference [25].

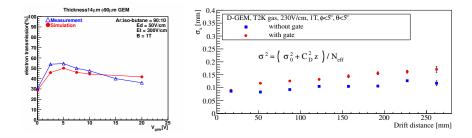

A first gate prototype using 14 µm thick GEM, with 90 µm holes and

140  $\mu$ m pitch was tested in 0 and 1 T magnetic fields. It showed a maximum transparency of 50 % in both cases. A consistent effect on the point resolution was observed. This transparency is too low for the performance requirements of the ILD TPC, and would probably be worse in a 3.5 T magnetic field.

Figure 3.4: Left: transparency measurement for the GEM gate prototype, for different applied voltages. A maximum is observed around 5 V. Right: measured point resolution with and without gate. At long drift distances, the resolution is reduced by a factor consistent with the expected value of  $\sqrt{2}$ .

A simulation study was performed in [25], to determine what are the limits in transparency of a GEM structure. The simulations, using Garfield++, shows that in a 3.5 T magnetic field, the geometrical aperture of the GEM is the main factor that determines its transparency to electrons. As can be seen in figure 3.5, the maximum transparency is very close to the geometrical aperture, and obtained for low voltages. In that configuration, the electric field distortions are minimal and the electrons follow the magnetic field lines.

Figure 3.5: Simulated electron transmission of a honeycomb gate with 81 % geometrical aperture in a 3.5 T magnetic field. Different transfer fields and GEM thicknesses were checked. The transparency does not depend much on these parameters and the maximum transparency is obtained at very low voltage and is almost equal to the geometrical aperture.

There are now ongoing studies at the company Fujikura to manufacture GEMs with very large aperture. A structure with 300 µm diameter hole,

and 330  $\mu m$  pitch (therefore offering about 70 % transparency) might be feasible, but could be expensive for large surfaces.

## 3.4 Conclusion

It has been shown that the ions from MPGD amplification in the ILD TPC can create sizable distortions of the drift field. The decision has been made to include a gating system to suppress this effect. A wire grid included in the readout module, with wires in the radial direction, should provide a good solution. Studies are still needed to build an appropriate mechanical structure, and to decide on the voltage configuration (single or alternate potential). Another solution using a dedicated GEM as a gate is still under consideration, but shows manufacturing difficulties and probably cannot offer transparency higher than 70 %.

## Chapter 4

# Electronics

## 4.1 Introduction

Several available electronics readout systems have been used prior to and during the EUDET-era, as for example STAR, AFTER from T2K and AL-TRO from ALICE. They have been adapted/improved to be used for the readout of MPGDs. However, none of them fulfill the requirements of the final front-end electronics and therefore further development is required and is presently ongoing. The future aim is to produce electronics that is compatible with the pad size given by physics goals of the ILC. The requirements are described in the following section. The past and ongoing integration efforts are then reviewed (cooling and power pulsing). In the last section an attempt is made to give a roadmap toward the design and production of a suitable electronics in time for the startup.

## 4.2 Requirements

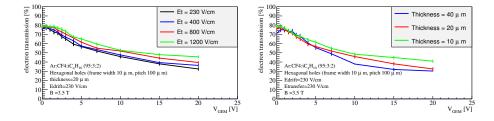

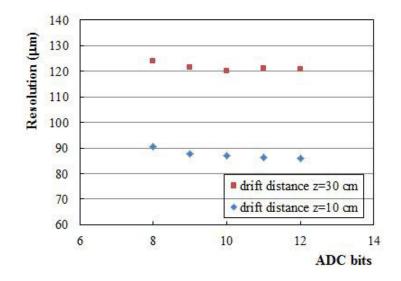

The electronics must be able to read full trains (2500 bunch crossings) at a 5 to 10 Hz frequency. It must realize a full wave sampling of each pad at a frequency which is consistent with the duration of the signal induced by a portion of a track on a padrow, that is 20 to 50 MHz. The ADC should be accurate enough to measure large fluctuations of the main pad and also the small signal of the neighboring pads to obtain the position accuracy. It was shown from test beam data [23] that down to 8-9 bit the space resolution is not significantly affected (see figure 4.1). The ILD TPC requires an unprecedented channel density. In the most demanding scheme, one channel must occupy an area of 4 mm<sup>2</sup> or more on the endplate, on average (taking into account space taken by the module frames, HV connections, etc.) and the total thickness of the front end electronics must be limited to 5 cm and 0.25 X<sub>0</sub>.

In order to be able to run the gas amplification at low gain, which min-

Figure 4.1: The resolution as measured from Micromegas test beam data, as a function of the number of ADC bits used (12 is the actual number of ADC bits and lower numbers are obtained by rounding up the amplitude to this accuracy).

imizes the problem with back-flowing ions, a low enough noise level for the front-end electronics has to be achieved. A goal of 600 electrons seems to be in reach, however with some trade-off with power consumption or shaping time. The shaping time should be kept as minimum for the z coordinate measurement and the 2-track separation, but values below 60-100 ns would not allow the full charge to be collected, because of longitudinal diffusion and other effects of comparable size. Thus, the aim is to operate the preamplifier with shaping times as short as 100 ns or 200 ns, irrespectively of the gas amplification technology (GEM or Micromegas). A power consumption below 8 mW per channel seems to be realistic, but power pulsing would be needed to bring the total power consumption to an acceptable 100 W/m<sup>2</sup>. Finally, in order to avoid dealing with useless information, an on-chip zero suppression with self-triggering and time stamping of the significant signals is necessary.

To first order, these requirements are comparable for both GEM and Micromegas, thus most of the electronics development can be done prior to the technology choice.

## 4.3 Test electronics

In going from small to large TPC prototypes, there was a need for test electronics to provide data which proved that the performance of the MPGDs could meet the physics goals of ILC. CERN and Lund developed an ALTRO- based system which was used for the tests with GEMs. This electronics evolved, first by using a new amplifier-shaper PCA16. And later the analogue and digital signal processing were integrated in the same chip resulting in the SALTRO16 chip, which is now in the process of being mounted on cards. In parallel to this effort, the T2K electronics was successfully used for tests of Micromegas + resistive coating. Then it was adapted to fit on the back of a module.

#### 4.3.1 The ongoing SALTRO16 development

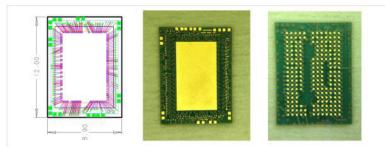

The SALTRO16-chip, developed at CERN, includes a very-low-noise amplifier and an integrated 10 bit ADC. It contains power pulsing features and is very compact. The LCTPC collaboration has obtained 610 such chips (210 as a contribution from CERN and 400 bought by Japanese groups). In order to achieve a significant reduction in size of the front end electronics, most modern techniques for circuit assembly are used. In almost all aspects, it led to stretch the techniques beyond what is used in industrial manufacturing today.

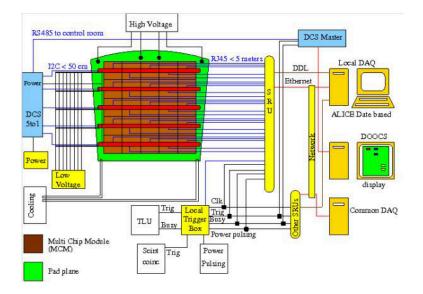

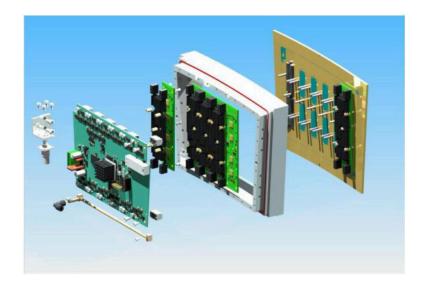

The SALTRO16 readout system is schematically shown in figure 4.2 for one pad module. It is a highly advanced development project, which includes several subsystems like the Carrier Board, the MCMboard, the Low Voltage Board, the Detector Control Boards, the Serial Readout and the Monitoring. A complication is that these subsystems are not independent but have to be developed in parallel. In order to facilitate testing and debugging of the various subsystems, it has in some cases been necessary to construct prototype systems to avoid complications due to the requirements of compactness or due to other constraints. The Carrier Board and the MCM-board are especially challenging due to the tight space limitation and the high precision required. The project has to be performed in collaboration with industry, which has the necessary competence and experience. Due to limited number of chips existing, the unknown chip yield and their high cost extreme care has to be taken to minimize the number of prototype steps and in the choice of industry partner to minimize the loss due to unpredictable fabrication yield.

The SALTRO16 chip combines the analogue and digital signal processing of the incoming charge. The silicon die itself is  $8.7 \times 6.2 \text{ mm}^2$  and contains 16 readout channels which equals an area of  $3.37 \text{ mm}^2$  per channel. The new chip can be turned off when no signals are expected, which drastically reduces the power consumption and the demands for cooling.

The alternative of using packaged chips is not a realistic choice since it requires too much space on the pad board in order to allow small enough pad sizes, although testing, mounting and service would be simpler. Due to the uncertainty in the yield it is unrealistic to assemble untested dies directly on a pad module with the requirement that all chips should work.

Figure 4.2: Schematic view showing the DAQ architecture of the SALTRO system.

Figure 4.3: Layout of the carrier board with bonding wires and passive components (left) together with photos of the top (middle) and bottom (right) surface, respectively, of one circuit board.

Instead the chips will be mounted on Carrier Boards, only slightly bigger than the chips themselves.

This facilitates the handling and allows for tests of individual chips. The size of the Carrier Boards is  $12.0 \times 8.9 \text{ mm}^2$ , which also includes space for bonding wires and some passive components. Eight of these Carrier Boards are soldered on one so called Multi Chip Module (MCM). The layout of the Carrier Board is shown in figure 4.2.

Recently 250 boards were delivered and figure 4.2 shows photos of the top and bottom surface, respectively, of one board. The yellow area on the top surface is where the SALTRO16 die will be glued.

The list of work in progress is kept up-to-date in reference [26] and

forthcoming versions.

The ongoing engineering phase aims at constructing a system that fulfills the various requirements of the final front-end electronics. The size of the electronics has been significantly reduced compared to the ALTROelectronics used for the demonstration phase and corresponds to a pad size of  $1 \times 8.5$  mm<sup>2</sup>. Cooling will be provided by a system based on two-phase CO<sub>2</sub>.

#### 4.3.2 Micromegas Integration

In parallel to this effort, a similar integration work has been carried out using the AFTER chips designed for the T2K Micromegas TPC readout. At the same time, the acquisition was upgraded from single module capability to multi-module (up to 12). This required a complete revision of the architecture from the Front End to the backend. This work has been described in reference [29].

The front-end part uses 72-channel AFTER chips to perform detector charge signal amplification, shaping, and waveform sampling in a 511timebin Switched Capacitor Array (SCA).

Following each detector signal sampling phase which is halted by an externally provided trigger signal, data stored in the SCAs are time-multiplexed and digitized at 20 MHz by multi-channel ADCs. Four AFTER chips are mounted on a Front-End Card (FECi) and six FECis are digitized and read out by a Front-End Mezzanine card (FEMi). Each FEMi communicates with a Data Concentrator Card (DCC) over a 2 Gbps duplex optical link. System settings, the global 100 MHz clock and trigger information are transported by the DCC to FEMi fiber while the acquired data and monitoring information travel over a second fiber stand.

By avoiding flat cables, the noise was reduced by 25 %, and the choice of a new ADC off the shelf allowed a 25 % saving in power consumption. Space was saved by wire-bonding directly the dies to FECis and by removing the protection diodes and resistances, the function of anti-spark protection being provided by the resistive-capacitive layer. Some of the passive components were transferred to the FEMi. Very flat 300 points connectors were used for the contact FECi-PCB, insuring dismountability. Single module data were taken in 2011, and 6 and 7 module data were taken in 2012 and 2013.

The plan is now to connect to the diphasic  $CO_2$  cooling system to replace the present air cooling. The AFTER chip also has power pulsing capability on the analog part.

Figure 4.4: A fully integrated Micromegas panel, where one sees the Module Mezzanine card (FEMi), the air cooling pipe, the Front End Cards equipped of their radiators (in black), all this fixed to the detector PCB.

## 4.4 Tentative Roadmap towards the ILD TPC electronics

None of the test electronics realized so far is fully satisfactory for the ILD TPC. The AFTER electronics is based on analog memories of the SCA type, and these are not likely to reach a depth of nearly 20,000 buckets which would be necessary for a full train registering. On the other hand, the present SALTRO16 electronics requires further packing and its power consumption has to be optimized. This is the reason why the GdSP project offers a realistic alternative. The chosen deep submicron technology might have to be one supported by industry in the next decade. According to specialists, this will not be the case of 130 nm, but probably 65 nm minimum channel length is to be targeted. Already an overview study of this technology has begun within the European AIDA consortium. Going to such a fine technology will naturally save space on the die, and the power consumption will probably be reduced as such chips work at a reduced voltage. On the other hand, this might limit the total dynamic range, which is however not critical in our application. Present noise estimates with the 130 nm technology in standard conditions are of the order of 600 electrons. This will be thoroughly tested in the coming CFE (Common Front End) foundry of AIDA, end of November 2013. The GdSP would keep the digital filter integrated as for the SALTRO, but would feature several supplied voltage levels that could be switched independently during the course of the data taking, to optimize the power consumption. However, the future support

for this project is at the moment uncertain.

The ADC will have to be fully redesigned to minimize its consumption. The question arises whether or not this has to be done already in 130 nm technology. Some limited work could allow a suitable off-the-shelf design to be found.

If we aim at a startup around end of 2026, there is no real point starting the design already now. It would become obsolete at the time of production. So we should refine the requirements on the basis of detailed simulations in the next few years. If we want to make soon a new chip for testing purposes, in 130 nm, it will be difficult to fulfill all the requirements and it will probably obsolete at the time of chip production (around 2022). Whether and when new test electronics is needed is thus an open question and requires serious studies. A group has to be formed inside the LCTPC collaboration to consult specialists on chip design.

# Chapter 5

# Mechanics

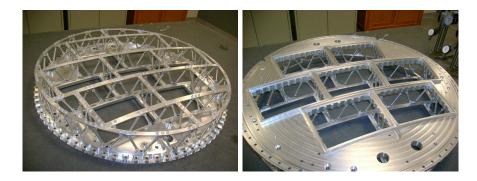

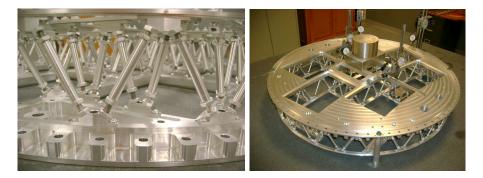

The mechanical design challenges for the ILD TPC, i.e. the field cage, the endplate and the cathode, are to reach a high mechanical and electrical stability while keeping the material budget in front of the outer detectors minimal.

The mechanical stability and accuracy is needed to ensure a very homogeneous electric field inside the sensitive volume. To reach the resolution goal of 100 µm for the point resolution respectively  $\delta(1/p_t) = 10^{-4} / \text{GeV/c}$ for the momentum resolution, the electric field has to be homogeneous to the level of  $\Delta E/E \leq 10^{-4}$ . The required electric stability results from the high fields used in the drift volume  $-\mathcal{O}(100) \text{ kV}$ , depending on the gas. Simulations showed that to keep energy loss in the TPC and conversions low to not significantly affect the calorimeter measurements and the particle flow reconstruction, the material budget has to be limited to 5% of a radiation lenght  $X_0$  in the barrel region and 25% at the endcaps.

After tests with smaller prototypes with a diameter of about 300 mm, the Large Prototype with an outer diameter of 770 mm has been built to study and develop the design and manufacturing techniques for the ILD TPC. In the following sections the status of the development of the field cage (section 5.1) and the endplate (section 5.2) are presented.

### 5.1 Design of a new Fieldcage

One goal of the development of the Large Prototype was to study the momentum resolution and dE/dx measurement as a logical step after feasibility and point resolution studies performed with small prototypes. In addition, the technical challenges are studied, such as how to build a lightweight and mechanically precise field cage, anode endplate and cathode on a larger scale.

The field cage of the Large Prototype has been built in cooperation with industry. It is made of composite materials including additional layers for field shaping and insulation. This allows for a lightweight structure while providing a high mechanical stability.

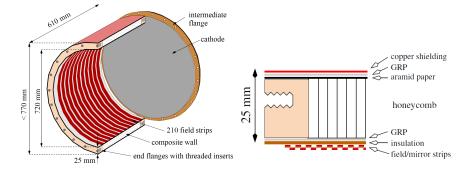

A schematic sketch of the field cage and the cathode is shown in figure 5.1. Its dimensions and a cut through the 25 mm thick wall is shown. Its length measures 610 mm —of which in operation about 570 mm are available as drift length— and an inner diameter of 720 mm. The material budget of the wall results in a radiation length of  $1.21\pm0.1\%$  of X<sub>0</sub>. The field shaping is done by a large, flexible printed circuit board with copper rings that divide the potential in small steps from cathode to anode. This board also has copper rings on the outer side to avoid distortions from the ground potential of the outer shielding layer. The current wall design has been tested for high voltage stability up to 30 kV. A more detailed description of the field cage and its construction can be found in [30].

Figure 5.1: Schematics of the Large Prototype field cage (left) and cut though the field cage wall including the end flange at the anode side (right).

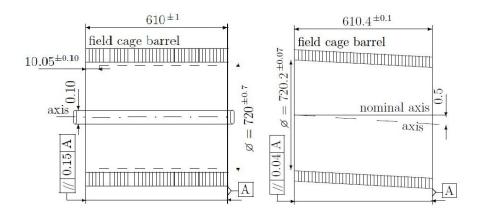

Due to a fabrication imperfection, the current field cage does not meet the accuracy specifications that are needed to ensure an electric field of the required homogeneity. The axis of the field cage barrel shows a shearing from the nominal axis of about 0.5 mm (figure 5.2), while 0.1 mm would have been acceptable for the needed field homogeneity. It was found that the reason for this shearing of the axis was an inaccurate mandrel on which the field cage was glued.

A second field cage is currently in development to correct the axis shearing. It is planned to build it in-house to gain experience with and have a better control of the production process. The mandrel has been worked over and measured so it fulfills now the precision requirements.

The new field cage will follow in most parts the design of the current one. However, some improvements besides the shearing correction are planned. The high voltage connection of the field shaping rings at the anode side will be re-designed based on experience gained during operation of the current field cage. This shall improve the high voltage stability and maintainability. Also, a further optimization of the material budget is planned. For this, it will be tested if some or all of the glass-fibre reinforced plastic (GRP)

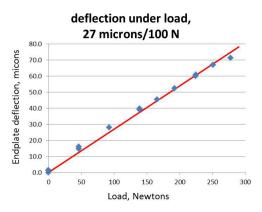

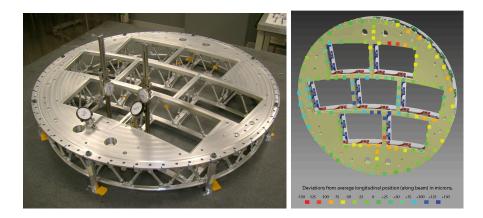

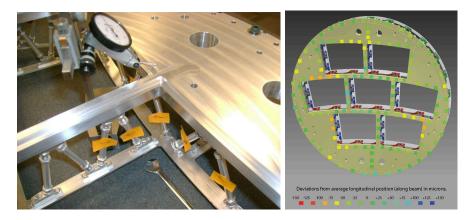

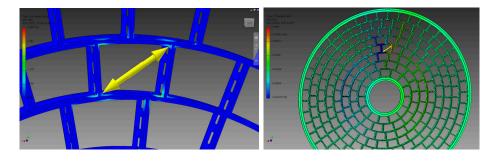

Figure 5.2: Dimension and precision specifications of the field cage (left) in comparison with the measured dimensions (right), showing the axis shearing.